ВИА Нано - VIA Nano

| |

| Общая информация | |

|---|---|

| Продается | VIA Technologies |

| Разработано | Кентавр Технологии |

| Общий производитель (и) | |

| Представление | |

| Скорость FSB | От 533 МГц до 1066 МГц |

| Кэш | |

| Кэш L1 | 64 КБ инструкций + 64 КБ данных на ядро |

| Кэш L2 | 1 МБ на ядро |

| Архитектура и классификация | |

| Мин. размер элемента | От 40 нм до 65 нм |

| Микроархитектура | ЧЕРЕЗ Исайю |

| Набор инструкций | x86-64 |

| Физические характеристики | |

| Ядра | |

| Пакет (ы) | |

| Продукты, модели, варианты | |

| Основное имя (я) | |

| История | |

| Предшественник | VIA C7 |

VIA Nano (ранее под кодовым названием VIA Isaiah ) представляет собой 64-битный процессор для персональных компьютеров . VIA Nano был выпущен компанией VIA Technologies в 2008 году после пяти лет развития путем ее разделения процессора, Centaur Technology . Эта новая 64-разрядная архитектура Isaiah была разработана с нуля, представлена 24 января 2008 года и запущена 29 мая, включая варианты с низким напряжением и торговую марку Nano. Процессор поддерживает ряд специфичных для VIA расширений x86, предназначенных для повышения эффективности устройств с низким энергопотреблением.

История

В отличие от Intel и AMD , VIA использует два разных кодовых названия для каждого ядра процессора. В этом случае кодовое имя «CN» использовалось в США компанией Centaur Technology. Библейские имена используются VIA в качестве кодов на Тайване , и Исайя был выбран для этого конкретного процессора и архитектуры. Ожидается, что VIA Isaiah будет в два раза быстрее по производительности с целыми числами и в четыре раза быстрее по производительности с плавающей запятой, чем VIA Esther предыдущего поколения при аналогичной тактовой частоте . Ожидается, что энергопотребление будет на уровне процессоров VIA предыдущего поколения с расчетной тепловой мощностью от 5 Вт до 25 Вт. Архитектура Isaiah представляет собой полностью новую конструкцию и поддерживает такие функции, как инструкции x86-64. set и виртуализации x86, которые были недоступны в его предшественниках, линейке VIA C7 , при сохранении их расширений шифрования. Несколько независимых тестов показали, что VIA Nano работает лучше, чем одноядерный Intel Atom, в различных рабочих нагрузках. В тесте Ars Technica 2008 года VIA Nano продемонстрировал значительную производительность в подсистеме памяти после того, как его CPUID был изменен на Intel, намекая на возможность того, что тестовое программное обеспечение проверяет только CPUID, а не фактические функции, поддерживаемые ЦП, для выбора пути кода. Используемое программное обеспечение для тестирования производительности было выпущено до выпуска VIA Nano.

3 ноября 2009 года VIA запустила серию Nano 3000. VIA утверждает, что эти модели могут предложить на 20% прирост производительности и на 20% большую энергоэффективность, чем серии Nano 1000 и 2000. Тесты, проведенные VIA, показывают, что процессор Nano серии 3000 с тактовой частотой 1,6 ГГц может превзойти устаревший Intel Atom N270 примерно на 40–54%. В серию 3000 добавлены расширения набора инструкций SSE4 SIMD , которые были впервые представлены в 45-нм версиях архитектуры Intel Core 2 .

11 ноября 2011 года VIA выпустила двухъядерный процессор VIA Nano X2 с их первой двухъядерной материнской платой pico-itx. VIA Nano X2 построен по 40-нм техпроцессу и поддерживает расширения набора инструкций SSE4 SIMD , критически важные для современных приложений, зависимых от операций с плавающей запятой. Via заявляет, что производительность на 30% выше по сравнению с Intel Atom с более высокой тактовой частотой на 50%.

В Zhaoxin совместного предприятия процессоры, выпущенные с 2014 года, основаны на серии VIA Nano.

Функции

- набор инструкций x86-64

- Тактовая частота от 1 ГГц до 2 ГГц

- Частота шины 533 МГц или 800 МГц (1066 МГц для Nano x2)

- Кэш L1 64 КБ данных и 64 КБ инструкций и кэш L2 1 МБ на ядро.

- 65 нм техпроцесс (40 нм для Nano x2)

- Суперскалярное выполнение инструкций вне очереди

- Поддержка набора инструкций MMX, SSE, SSE2, SSE3, SSSE3 и SSE4

- Поддержка виртуализации x86 с Intel-совместимой реализацией (отключена перед шагом 3)

- Поддержка памяти ECC

- Совместимость по выводам с VIA C7 и VIA Eden

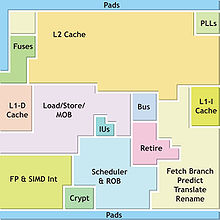

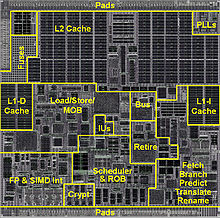

Обзор архитектуры

- Неупорядоченный и суперскалярный дизайн : обеспечивает гораздо лучшую производительность, чем его предшественник, процессор VIA C7, который был исправен. Это ставит архитектуру Isaiah в соответствие с предложениями AMD и Intel того же года.

- Слияние инструкций : позволяет процессору объединять некоторые инструкции в одну инструкцию, снижая требования к питанию и обеспечивая более высокую производительность (Atom использует аналогичную стратегию для обработки инструкций x86 более `` целостным '' образом, вместо того, чтобы разбивать их на RISC-подобные микроконтроллеры. -опс).

- Улучшенное предсказание ветвлений : использует восемь предикторов на двух этапах конвейера.

- Конструкция кэша ЦП : эксклюзивная конструкция кэша означает, что содержимое кэша L1 не дублируется в кэше L2, обеспечивая больший общий объем кеша.

-

Предварительная выборка данных : включение новых механизмов предварительной выборки данных, включая как загрузку специального 64-строчного кеша перед загрузкой кеша L2, так и прямую загрузку в кеш L1.

- Получает 4 инструкции x86 за цикл, в отличие от 3-5 инструкций Intel.

- Выдает 3 микрооперации / такт исполнительным блокам

- Доступ к памяти : объединение небольших хранилищ с большими загрузочными данными.

-

Блоки исполнения: доступно семь блоков исполнения, что позволяет выполнять до семи микроопераций за такт.

- 2 Целочисленные единицы (ALU1 и ALU2)

- ALU1 является полнофункциональным, в то время как ALU2 не имеет некоторых малоиспользуемых инструкций и поэтому больше подходит для таких задач, как вычисление адресов.

- 2 устройства хранения, одно для хранилища адресов и одно для хранилища данных в соответствии с VIA .

- 1 единица нагрузки

- 2 мультимедийных блока (MEDIA-A и MEDIA-B) с каналом передачи данных шириной 128 бит , поддерживающим 4 операции с одинарной точностью или 2 операции с двойной точностью. Вычисление мультимедиа относится к использованию 2 единиц мультимедиа.

- MEDIA-A выполняет инструкции «сложения» с плавающей запятой (2-тактовая задержка для одинарной и двойной точности ), целочисленное SIMD, шифрование, деление и извлечение квадратного корня.

- MEDIA-B выполняет инструкции «умножения» с плавающей запятой (2-тактовая задержка для одинарной точности, 3-тактовая задержка для двойной точности).

- Из-за параллелизма, представленного с 2 модулями мультимедиа, вычисление мультимедиа может обеспечивать четыре инструкции «сложить» и четыре инструкции «умножения» за такт.

- Новая реализация FP-сложения с самой низкой тактовой задержкой для процессора x86 на данный момент.

- Почти все целочисленные инструкции SIMD выполняются за один такт.

- Реализует наборы мультимедийных инструкций MMX , SSE , SSE2 , SSE3 , SSSE3.

- Реализует набор мультимедийных инструкций SSE4.1 (серия VIA Nano 3000)

- Реализует набор мультимедийных инструкций SSE4.1 (серия VIA Nano x2)

- 2 Целочисленные единицы (ALU1 и ALU2)

-

Управление питанием : помимо очень низкого энергопотребления, добавлено много новых функций.

- Включает новое состояние питания C6 (кеши очищены, внутреннее состояние сохраняется, а напряжение ядра отключено).

- Адаптивное управление состоянием P : переход между состояниями производительности и напряжения без остановки выполнения.

- Адаптивный разгон: автоматический разгон при низкой температуре ядра процессора.

- Adaptive Thermal Limit : регулировка процессора для поддержания заданной пользователем температуры.

-

Шифрование : включает движок VIA PadLock.

- Аппаратная поддержка шифрования AES , безопасных алгоритмов хеширования SHA-1 и SHA-256 и генерации случайных чисел

Примерно 31.08.2014 появились слухи о возможном обновлении Исайи II.

Смотрите также

использованная литература

внешние ссылки

Нажмите

- «Битва маломощных процессоров: лучший выбор для неттопа» . 27 сентября 2008 г. Архивировано из оригинала на 2013-10-25.

- «Матч за недовольство младших классов: Нано против Атома» . 2008-07-30.

- «Nano L2100 от Via превосходит Intel Atom 230» . 2008-07-30.